### Sensoren und Aktoren

### Wahlpflichtfach 5. Semester Elektrotechnik

Prof. Dr. Felix Hüning

FB Elektrotechnik und Informationstechnik FH Aachen

Die Folien sind für den persönlichen Gebrauch im Rahmen des Moduls gedacht. Eine Veröffentlichung oder Weiterverteilung an Dritte ist nicht gestattet (F. Hüning)

#### **Examples**

- Frequently used data busses for short range communication

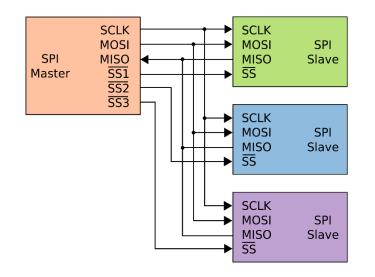

- SPI: Serial Peripheral Interface

- I<sup>2</sup>C: Inter-Integrated Circuit

Von en:user:Cburnett - Own work made with Inkscape, CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=1472017

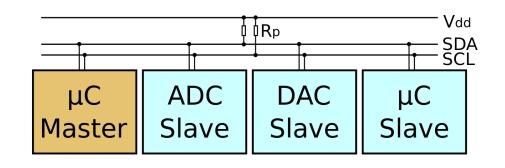

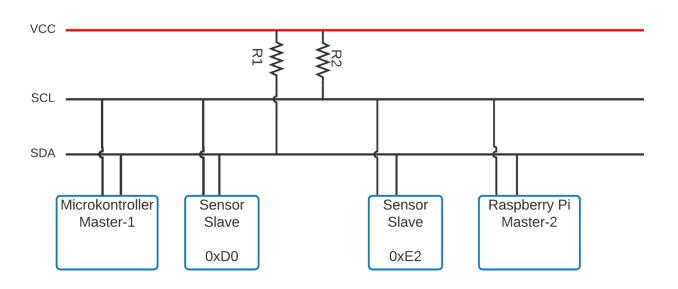

#### I<sup>2</sup>C-Bus

- 2 lines

- SCL clock (driven by master)

- SDA data line

- Open drain: Pull-up resistors to VCC

- Active low: units pull line to GND

- Standard: <u>https://www.nxp.com/docs/en/user-guide/UM10204.pdf</u>

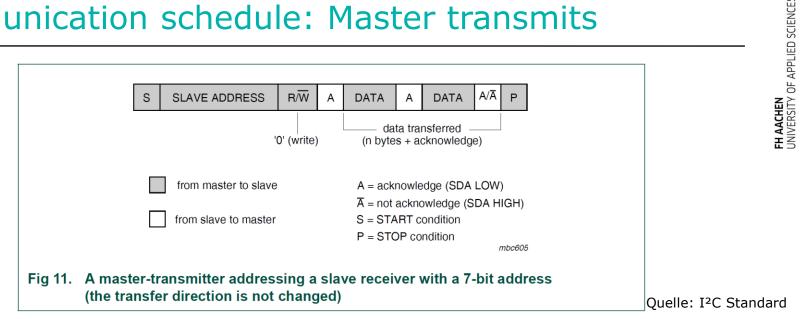

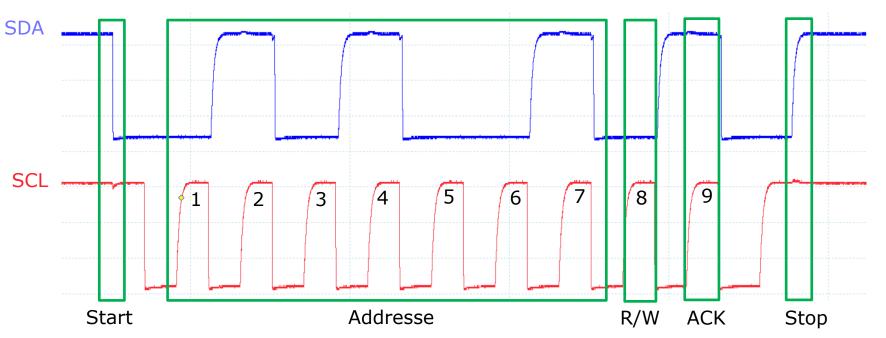

#### Communication schedule: Master transmits

- Master starts communication (Start-Condition)

- Master sends slave addresse (7Bit)

- Master indicates transmit or receive: (RW-Bit)

- Slave sends acknowledgment (Acknowledge, ACK)

- Master send data in 8 Bit units, Slave acknowledges by ACK

- End of transfer by master (Stop-Condition)

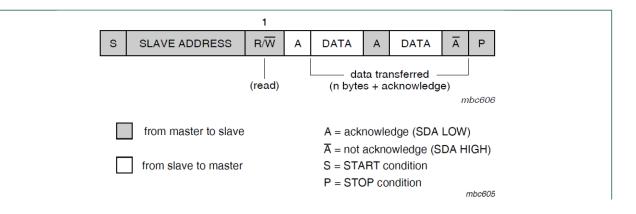

#### Communication schedule: Slave transmits

Quelle: I<sup>2</sup>C Standard

- Master starts communication (Start-Condition)

- Master sends slave addresse (7Bit)

- Master indicates transmit or receive: (RW-Bit)

- Slave sends acknowledgment (Acknowledge, ACK)

- Slave sends data in 8 Bit units, Master acknowledges

- After last data byte: Master sends NACK

- Master stops communication (Stop-Condition)

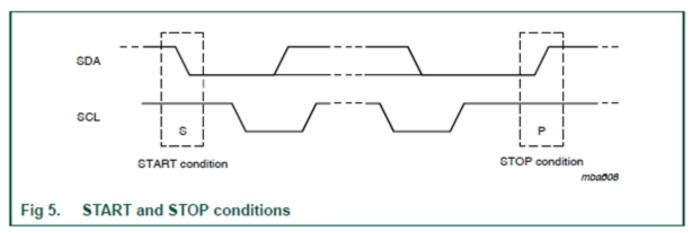

#### Start and stop condition

Quelle: I<sup>2</sup>C Standard

Bus not busy: SDA and SCL are HIGH

#### Start condition:

- Master pulls SDA to LOW

- SCL stays HIGH

#### Stop condition:

- SDA is pulled to HIGH

- At the same time SCL is HIGH

H AACHEN JNIVERSITY OF APPLIED SCIENCES

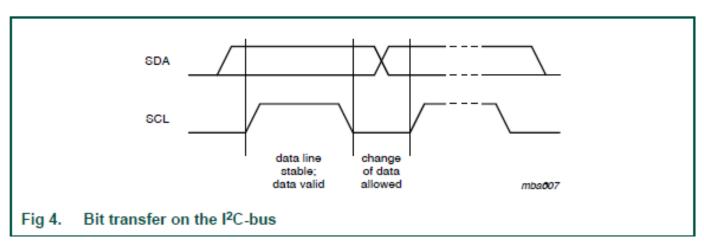

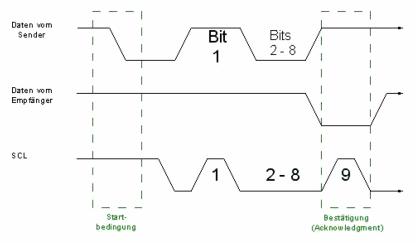

#### Validity of bits

Quelle: I<sup>2</sup>C Standard

- During data transmission: Changes of SDA during Clock LOW only

- Start und Stop condition

- Clock HIGH and SDA level changes

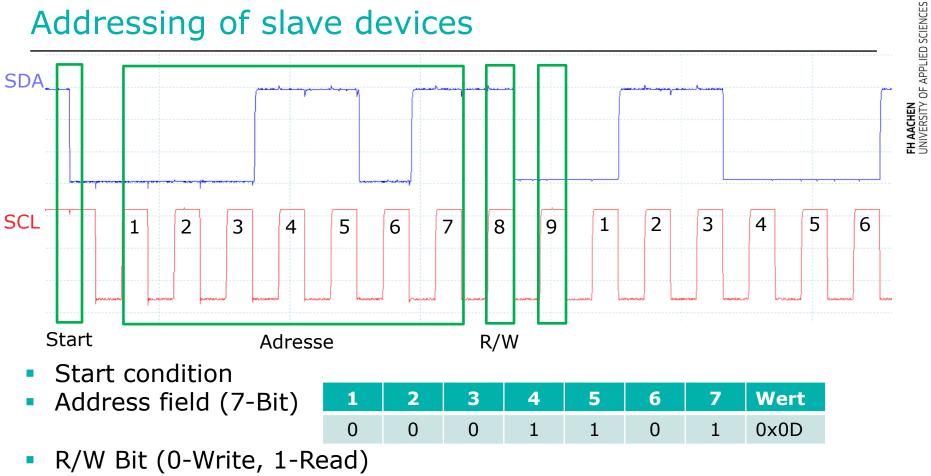

#### Addressing of slave devices

ACK by slave: slave pulls SDA to LOW

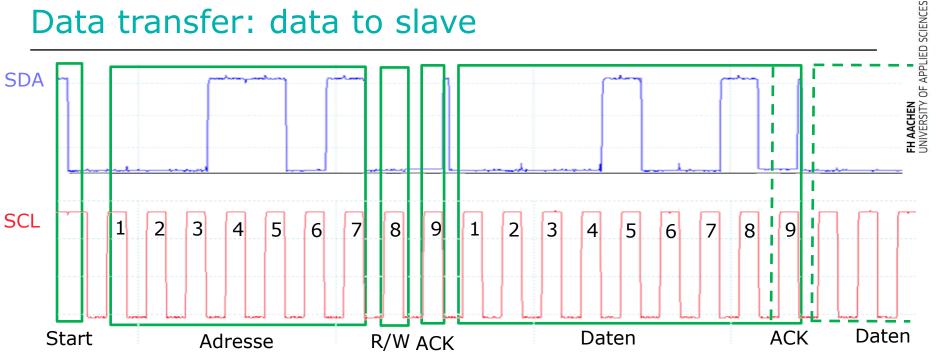

#### Data transfer: data to slave

- Start condition

- Address field (7-Bit) + R/W Bit (0-Write, 1-Read) + ACK

- 1 or more 8-Bit data fields + ACK/NACK Data sent: **b00001001** oder **0x09**

- Stop condition

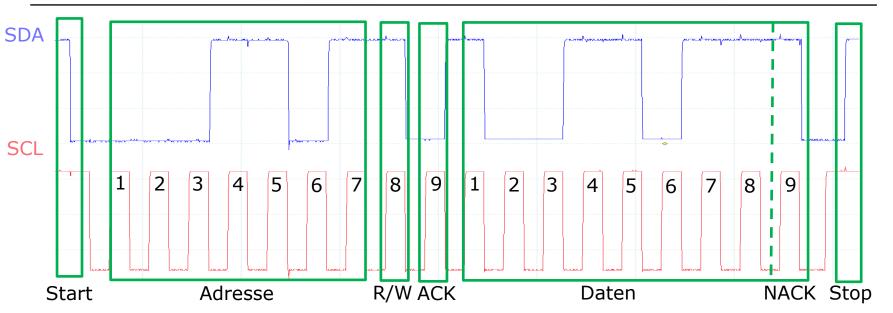

#### Data transfer: data from slave

- Start condition

- Address field (7-Bit) + R/W Bit (0-Write, 1-Read) +ACK

- 1 or more 8-Bit data fields + ACK/NACK

Data from sensor: b1001 1011 = 0x9B

- Stop condition

FH AACHEN UNIVERSITY OF APPLIED SCIENCES

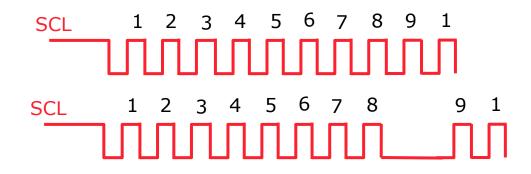

#### Communication

- Start

- Addresse + R/W-Bit from master

- Receiver ties SDA to LOW for one clock cycle (ACK) (9. cylce)

- ACK mandatory for all but the last byte

Bild [10]: Bestätigung bei der Datenübertragung Quelle: Roboternetz.de

## **FH AACHEN** UNIVERSITY OF APPLIED SCIENCE<sup>3</sup>

#### ACK, NACK and No ACK

ACK (SDA is LOW) by receiver

- At the end of a data transfer to the master the master sends NACK (SDA = HIGH), indicating all data were received

- Reasons for missing ACK (no ACK)

- No device with given address available

- Missing synchronization (e.g. slave missed one clock cycle)

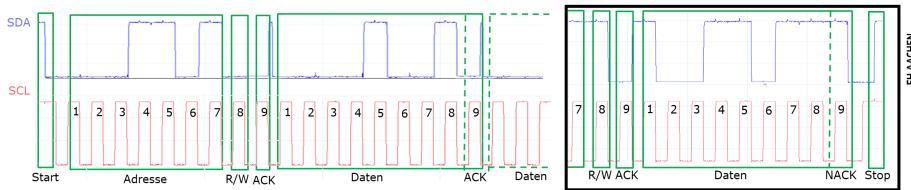

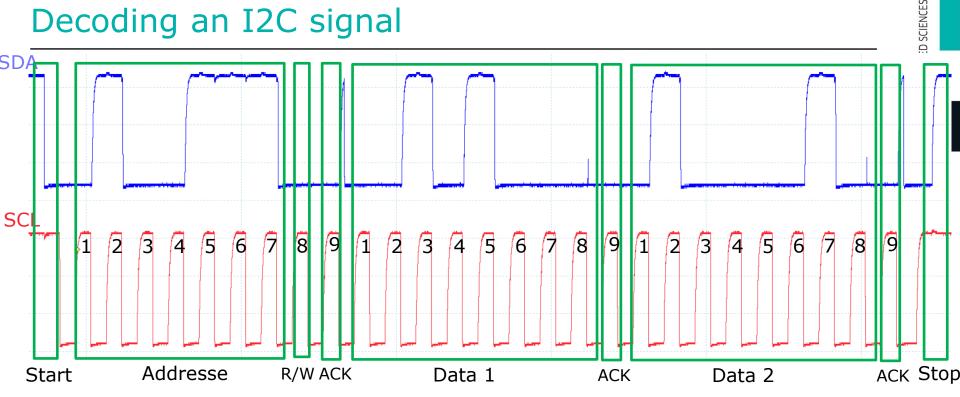

#### Decoding an I2C signal

- Address: b0101001 = 0x29

- R/W: Low, Write: Master sends to Slave

- No ACK from Slave

- Stop condition

- No response from slave, wrong addresse or slave not connected

#### Decoding an I2C signal

- Address: b0100111 = 0x27

- R/W: Low, Write: Master sends to slave + ACK from slave

- Data1:  $b0010 \ 1000 = 0x28 + ACK$  from Slave

- Data2:  $b0100\ 0010 = 0x42 + ACK$  from Slave

- Stop condition

- Valid data transfer

#### Additional features of the standard

Additional features of I2C

- Different data rates (Fast Mode, High Speed, ... )

- 10-Bit addressing and subadressierung

- Multi-Master-Mode

- Repeated Start-Signal

- Clock Streching

#### Data rates

|                 | Datenrate        |                |  |  |

|-----------------|------------------|----------------|--|--|

| Standard Mode   | Up to 100kbit/s  | Bidirectional  |  |  |

| Fast Mode       | Up to 400kbit/s  | Bidirectional  |  |  |

| Fast mode+      | Up to 1 Mbit/s   | Bidirectional  |  |  |

| High Speed Mode | Up to 3.4 Mbit/s | Bidirectional  |  |  |

| Ultra Fast Mode | Up to 5.0 Mbit/s | Unidirectional |  |  |

- Most sensors supprt Standard Mode

- Fast Mode, Fast Mode+ and High-speed devices are downward compatibel

- Ultra-Fast Mode is not downward compatible

#### Communication: addressing

- I<sup>2</sup>C addresses are often device specific

- Same devices on on bus system: address is split into fixed address and sub-address

|         | Fixed address |   |   |   | Sub-address |   |   |  |

|---------|---------------|---|---|---|-------------|---|---|--|

| Adresse | 0             | 0 | 1 | 0 | x           | x | x |  |

- Fixed address of device (4bit) and sub-addresse (3bit)

- Adressing via solder option or jumper

#### Communication: dedicated addresses

X = don't care; 1 = HIGH; 0 = LOW.

| Slave address | R/W bit | Description                                      |

|---------------|---------|--------------------------------------------------|

| 0000 000      | 0       | general call address <sup>[1]</sup>              |

| 0000 000      | 1       | START byte <sup>[2]</sup>                        |

| 0000 001      | Х       | CBUS address <sup>[3]</sup>                      |

| 0000 010      | Х       | reserved for different bus format <sup>[4]</sup> |

| 0000 011      | Х       | reserved for future purposes                     |

| 0000 1XX      | Х       | Hs-mode master code                              |

| 1111 1XX      | 1       | device ID                                        |

| 1111 0XX      | Х       | 10-bit slave addressing                          |

- General call address: Used for reset, address transmission

- Start Byte: High frequency polling for devices polling the bus

- Device ID: Read supplier and device ID

- 10-bit adressing

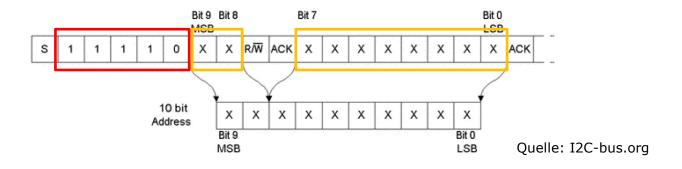

#### Communication: 10bit addressing

- Indicator for 10 bit addressing

- First 2 bits of 10 bit address

- R/W bit and Ack

- First data field with remaining 8 bit of 10 bit address

#### **Multi-Master**

- Has to be supported by all nodes

- Mixed singel and multi master devices may lead to disturbed communication

- Mutli-Master devices sense SCL and SDA

- Check whether bus is free (> 4.7 ns High)

- Wait for stop condition before start of transmission

- Interruption of transmission in case of an unexpected low level

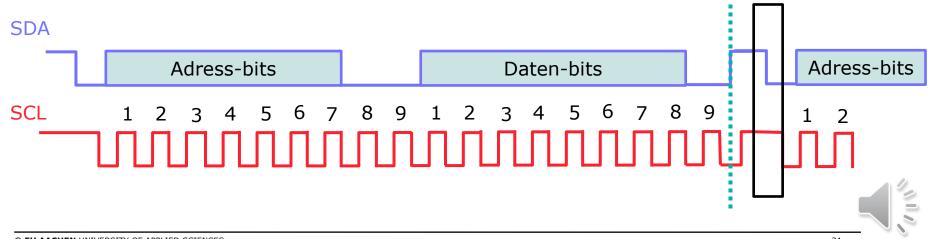

#### Repeated Start (Sr)

- Start without previous stop

- Read and write alternating (without releasing the bus)

- Example: Read memory

- 1. Master writes address of memory cell (I<sup>2</sup>C Write)

- 2. Master reads memory from slave (I<sup>2</sup>C Read)

- Stop condition between 1. and 2. would release the bus

- Another master can start access

- Race condition

# FH AACHEN UNIVERSITY OF APPLIED SCIENCES

#### **Clock Stretching**

- Option to stop or delay I2C communication

- Slave ties clock to low

- Slave has more time to send Ack

#### Troubleshooting

- No communication

- Possible reasons:

- Bus seems busy (SDA and SCL not HIGH)

- Unexpected restart of MCU (Master) during communication

- Electromagnetic disturbance

- Slave waits for missing clock signals

- Slave doesn't react on start condition

- Remedy: Send several clock signals (e.g. 16) and stop signal after reset to put slave back to receive mode

#### Troubleshooting:

- Occasionally no ACK from Slave

- Possible reasons:

- Signal levels are not reached in time (to slow)

- Slave misses one or more clock cycles

- Electromagnetic disturbance was read as clock cycle

- Check signal level and rise and fall time wrt specification

- Remedy: Modification of pull-up resistors

H AACHEN JNIVERSITY OF APPLIED SCIENCES

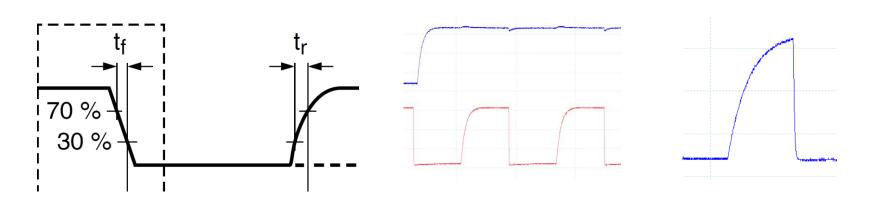

#### Fall and Rise Time:

- Signal edges have to be in line with specification

- System setup important (devices, cable length, pull up resistors)

- Longer cable, more devices, pull up resistors with high resistance increase rise time

- If t<sub>r</sub> is to big final signal level is not reached in time

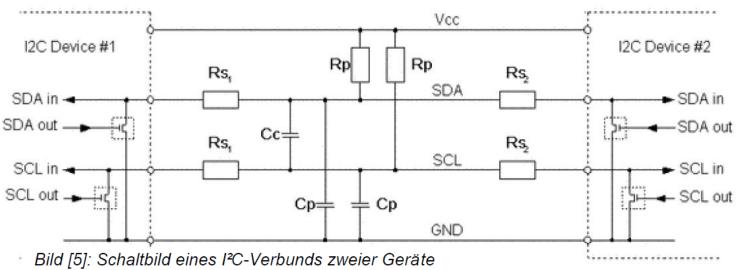

#### **Electrical characteristics**

Quelle: I<sup>2</sup>C-bus.org

#### Zugehörige Abkürzungen:

| VCC | Versorgungsspannung, typischerweise von 1,2 – 1,5 V                |  |  |  |

|-----|--------------------------------------------------------------------|--|--|--|

| GND | Masse (Ground)                                                     |  |  |  |

| SDA | I <sup>2</sup> C Datenleitung (serial data)                        |  |  |  |

| SCL | I <sup>2</sup> C Taktleitung (serial clock)                        |  |  |  |

| Rp  | Pull-up Widerstand, auch I <sup>2</sup> C Terminator/Endwiderstand |  |  |  |

| Rs  | serieller Widerstand                                               |  |  |  |

| Ср  | Leitungskapazität (eines Kondensators)                             |  |  |  |

| Cc  | Kondensator                                                        |  |  |  |

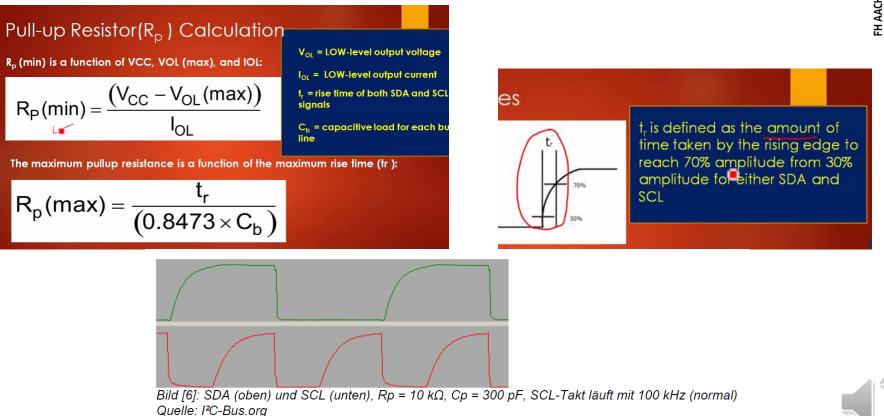

#### Specification pull up calculation

| Symbol Parameter                                  | Parameter                                                   | Conditions                                             | Standard-mode      |                     | Fast-mode                         |        | Fast-mode Plus                                   |                  | Unit |

|---------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------|--------------------|---------------------|-----------------------------------|--------|--------------------------------------------------|------------------|------|

|                                                   |                                                             |                                                        | Min                | Мах                 | Min                               | Мах    | Min                                              | Max              | -    |

| f <sub>SCL</sub>                                  | SCL clock frequency                                         |                                                        | 0                  | 100                 | 0                                 | 400    | 0                                                | 1000             | kHz  |

| t <sub>HD;STA</sub>                               | hold time (repeated) START condition                        | After this period, the first clock pulse is generated. | 4.0                | -                   | 0.6                               | -      | 0.26                                             | -                | μs   |

| tLOW                                              | LOW period of the SCL clock                                 |                                                        | 4.7                | -                   | 1.3                               | -      | 0.5                                              | -                | μs   |

| thigh                                             | HIGH period of the SCL clock                                |                                                        | 4.0                | -                   | 0.6                               | -      | 0.26                                             | -                | μs   |

| t <sub>su;sta</sub>                               | set-up time for a repeated START condition                  |                                                        | 4.7                | -                   | 0.6                               | -      | 0.26                                             | -                | μs   |

| t <sub>HD;DAT</sub> data hold time <sup>[2]</sup> | CBUS compatible masters (see Remark in <u>Section 4.1</u> ) | 5.0                                                    | -                  | -                   | -                                 | -      | -                                                | μs               |      |

|                                                   | I <sup>2</sup> C-bus devices                                | 0[3]                                                   | _[4]               | 0[3]                | _[4]                              | 0      | -                                                | μs               |      |

| t <sub>SU;DAT</sub>                               | data set-up time                                            |                                                        | 250                | -                   | 100[5]                            | -      | 50                                               | -                | ns   |

| t <sub>r</sub>                                    | rise time of both SDA and SCL signals                       |                                                        | -                  | 1000                | 20                                | 300    | -                                                | 120              | ns   |

| t <sub>f</sub>                                    | fall time of both SDA and SCL signals[3][6][7][8]           |                                                        | -                  | 300                 | 20 ×<br>(V <sub>DD</sub> / 5.5 V) | 300    | 20 ×<br>(V <sub>DD</sub> / 5.5 V) <sup>[9]</sup> | 120 <sup>8</sup> | ns   |

| t <sub>SU;STO</sub>                               | set-up time for STOP condition                              |                                                        | 4.0                | -                   | 0.6                               | -      | 0.26                                             | -                | μs   |

| t <sub>BUF</sub>                                  | bus free time between a STOP and START condition            |                                                        | 4.7                | -                   | 1.3                               | -      | 0.5                                              | -                | μs   |

| Cb                                                | capacitive load for each bus line <sup>[10]</sup>           |                                                        | -                  | 400                 | -                                 | 400    | -                                                | 550              | pF   |

| t <sub>VD;DAT</sub>                               | data valid time <sup>[11]</sup>                             |                                                        | -                  | 3.45 <mark>4</mark> | -                                 | 0.9[4] | -                                                | 0.45[4]          | μs   |

| t <sub>VD;ACK</sub>                               | data valid acknowledge time[12]                             |                                                        | -                  | 3.45[4]             | -                                 | 0.9[4] | -                                                | 0.45[4]          | μs   |

| ∨ <sub>nL</sub>                                   | noise margin at the LOW level                               | for each connected device<br>(including hysteresis)    | 0.1V <sub>DD</sub> | -                   | 0.1V <sub>DD</sub>                | -      | 0.1V <sub>DD</sub>                               | -                | V    |

| ∨ <sub>nH</sub>                                   | noise margin at the HIGH level                              | for each connected device<br>(including hysteresis)    | 0.2V <sub>DD</sub> | -                   | 0.2∨ <sub>DD</sub>                | -      | 0.2V <sub>DD</sub>                               | -                | V    |

Specification I2C: max\_t<sub>r</sub> = 1000 ns, max t<sub>f</sub>=300 ns

#### Specification pull up calculation

- Spezifikation I2C: max\_trise = 1000ns, V\_OL = 0.4V

- Cb: Measured or from data sheet

FH Aachen Fachbereich Elektrotechnik und Informationstechnik Prof. Dr. rer. nat. Felix Hüning Eupener Straße 70 52066 Aachen T +49 (0)241 6009 51979 F +49 (0)241 6009 52191 huening@fh-aachen.de www.huening.fh-aachen.de